作为HDS的VSP主要的竞争对手之一,EMC在去年推出了Scale-Out的存储系统V-Max,这是EMC的Symmetrix家族第一个也是目前为止唯一的一个抛弃了DMX- Direct Matrix(直连矩阵)架构的产品。

V-Max采用Virtual Matrix(虚拟矩阵)架构,由V-Max引擎构成,每一个V-Max引擎都包括完整的128GB全局缓存、前端/后端IO接口以及处理器组件(V-Max 引擎包括缓存、前端连接和后端连接,是 Symmetrix V-Max 系统的基础。),形成一个完整的节点。

V-Max的扩展除了通过驱动器和缓存之外,还支持横向扩展技术,提供从一个引擎到最多8个引擎的扩展能力,每个V-Max引擎之间,通过外部交换网络(RapidIO)连接,任何一个引擎都可以连接其它的引擎,Virtual Matrix(虚拟矩阵)架构的节点间通信的带宽为24GB/s。

EMC方面表示,V-Max的8个引擎,“具有完全共享的连接、处理和容量资源”

与V-Max相对应,HDS的VSP采用的“一个特殊的建造的存储引擎(HDS公司CTO Hu Yoshida言)”,与EMC从DMX-4到V-Max的变化不同,其并非是对“上一代产品USP V的彻底的颠覆(或者称是一个激进的修改版)”,VSP的架构基于第五代的Cross bar交换架构,新的ASIC芯片被用于连接主机的前端导向器和连接磁盘的后端导向器(Front-end director,FED和Back-end directorBED),同时,系统内还应用了英特尔至强处理器(由于目前HDS方面并未具体披露型号,公开渠道所获得的资料又非常有限,因此目前尚不确定具体的核数和型号,只知道频率为2.33GHz)。

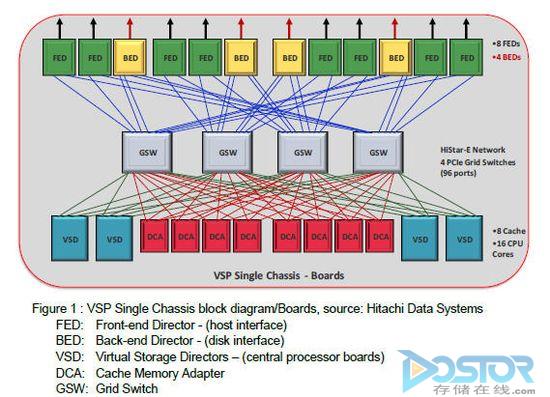

在一台VSP中(HDS成为Cluster0 或Controller 0),具体架构分为上下部分:上半部分为磁盘,支持2.5寸或3.5寸的SAS或SSD盘,下半部分为处理器单元。

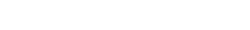

VSP的架构图,从现实情况看,就是下图所示

与VSP相比,EMC更加渲染其V-Max的开放性,突出其采用英特尔处理器——这一业界标准X86硬件——而淡化其是否采用或如何采用ASIC处理器技术。今年EMC推出的VPLEX存储虚拟化引擎已经被证明在今年第四季度将发布基于V-Max的版本,利用X86通用处理器,EMC称其产品能够获得技术发展曲线上的优势。

不过,也有人对V-Max究竟在哪些工作上采用ASIC芯片,哪些采用X86处理器表示疑问,由于对于重复性的工作,比如RAID,ASIC作为专门目的而设计的集成电路有天然的优势,没有理由完全抛弃而改用X86,对此,经过查询,在互联网上查到了有关V-Max的ASIC的这样一句话:EMC ASIC to handle the global memory access,而有关英特尔至强处理器的利用,则可以在如下完整资料中看到:

2 quad-core Xeon 2.3GHz (5400) processors

16 host channels (8 per Xeon processor)

16 drive channels (8 per Xeon processor)

128GB of global memory

EMC ASIC to handle the global memory access

RapidIO interconnect endpoints

HDS的VSP仍然较多的采用其专有的硬件架构、ASIC和接口,其提供的功能,如Scale-Out和纵深扩展,都基于其自身的内部架构,HDS方面认为,这样做能够使得他们提供更好的性能和更紧密集成的功能。

在VSP中,HDS提供了“3D”扩展能力——除了传统的Scale-up和Scale-Out,纵深扩展,连接业界竞争友商的产品,形成虚拟化存储池是其3D扩展的重要组成部分。

V-Max的架构,一共八个节点,通过RapidIO连接

在V-Max中,EMC将每个节点独立开来,提供平等但隔离的节点连接方法,当然也没有提供处理器升级扩展的功能。在VSP中,FED、BED、VSD和DCA(Cache Memory Adapter)都可以进行相对独立的扩展,而不需要依赖其他组件的增加,每一个都可以按照所能支持的最大比例装入控制器底板,并且整套VSP可以由1套控制器柜添加到两个。

由于架构上的不同,V-Max更依赖外部的,具有一套完整系统的节点的连接扩展,依靠其独立节点外的RapidIO,VSP则依赖其Cross bar交换架构,将多个BED、FED、DCA和VSD“大系统的内部连接”方式连接在一起,在VSP中,BED、FED和VSD、DCA(Cache Memory Adapter)通过HiStar-E网络通信,共计4个基于PCIE的Grid Switch共计96个端口。

基于VSP内部的Cross bar交换架构,每一个VSD都连接所有的GSW,拥有四条连接,每一个DCA也拥有四条连接到GSW,4个BED每个都拥有4条连接,但是只连接其中两个GSW,每个BED都用两条连接连接一个GSW,而每个FED则分别以一条连接到两个GSW。在VSP中,由于对GSW的4条连接,每一个VSD都能够访问任何CAs、BED或是FED以获得必须要的IO,因此,需要在VSD之间移动IO的情况大大减少,VSP内部拥有一个全局化的IO池,让BED、FED和VSD分享所有的IO。

在10月27日举行的2010日立数据存储科技峰会上,亚太区解决方案和产品事业部总监Phil Gann曾向记者提到,与V-Max的架构相比,VSP是紧耦合的,而V-Max是松散耦合的,他认为,VSP的控制器之间的数据交换效率更高、处理器的利用率会更高,V-Max每个节点之间的数据共享是不充分的,所以VSP才不像V-Max一样要使用八个节点,而是设计了两个节点的架构。

我们一直都在努力坚持原创.......请不要一声不吭,就悄悄拿走。

我原创,你原创,我们的内容世界才会更加精彩!

【所有原创内容版权均属TechTarget,欢迎大家转发分享。但未经授权,严禁任何媒体(平面媒体、网络媒体、自媒体等)以及微信公众号复制、转载、摘编或以其他方式进行使用。】

微信公众号

TechTarget

官方微博

TechTarget中国

作者

相关推荐

-

戴尔EMC推出全闪存PowerMax替代VMAX,内置NVMe

戴尔公司在今天举办的全球技术大会上,推出了EMC全闪存存储升级产品,支持非易失性闪存阵列(NVMe),迈出了意 […]

-

Dell EMC合并一周年回顾

在并购交易结束12个多月后,我们的专家对Dell收购EMC ,有史来最大的存储技术合并进行了评估。

-

EMC:商业无人机存储市场准备起飞

EMC想要在无人机相关的可扩展存储领域撑起一个小的立足点,特别是针对其横向扩展Isilon NAS和基于对象的弹性云存储产品。

-

HDS:聚焦未来的投资“冻结”

最近一家日本IT网站报道的有关HDS冻结对高端存储产品的投资一事引发众议。让人陷入疑惑的这次声明就是,HDS认为单纯的阵列产品并非企业存储的未来。